# **Exposing Cache Timing Side-Channel Leaks through Out-of-Order Symbolic Execution**

SHENGJIAN GUO\*, Baidu Security, USA

YUEQI CHEN\*, Pennsylvania State University, USA

JIYONG YU, University of Illinois at Urbana-Champaign, USA

MENG WU, Ant Group, China

ZHIQIANG ZUO, State Key Lab. for Novel Software Technology, Nanjing University, China

PENG LI, Baidu Security, USA

YUEQIANG CHENG, Baidu Security, USA

HUIBO WANG, Baidu Security, USA

As one of the fundamental optimizations in modern processors, the *out-of-order* execution boosts the pipeline throughput by executing independent instructions in parallel rather than in their program orders. However, due to the side effects introduced by such microarchitectural optimization to the CPU cache, secret-critical applications may suffer from timing side-channel leaks. This paper presents a symbolic execution-based technique, named SymO<sub>3</sub>, for exposing cache timing leaks under the context of *out-of-order* execution. SymO<sub>3</sub> proposes new components that address the modeling, reduction, and reasoning challenges of accommodating program analysis to the software code *out-of-order* analysis. We implemented SymO<sub>3</sub> upon KLEE and conducted three evaluations on it. Experimental results show that SymO<sub>3</sub> successfully uncovers a set of cache timing leaks in five real-world programs. Also, SymO<sub>3</sub> finds that, in general, program transformation from compiler optimizations shrink the surface to timing leaks. Furthermore, augmented with a speculative execution modeling, SymO<sub>3</sub> identifies five more leaky programs based on the compound analysis.

CCS Concepts: • Security and privacy  $\rightarrow$  Software and application security; • Software and its engineering  $\rightarrow$  Software verification and validation.

Additional Key Words and Phrases: Out-of-order execution, cache timing, side-channel leak, symbolic execution

# **ACM Reference Format:**

Shengjian Guo, Yueqi Chen, Jiyong Yu, Meng Wu, Zhiqiang Zuo, Peng Li, Yueqiang Cheng, and Huibo Wang. 2020. Exposing Cache Timing Side-Channel Leaks through Out-of-Order Symbolic Execution. *Proc. ACM Program. Lang.* 4, OOPSLA, Article 147 (November 2020), 32 pages. https://doi.org/10.1145/3428215

# 1 INTRODUCTION

In modern processor chips, CPU cache alleviates the outstanding speed disparity between the processor and the main memory. Generally, processors buffer the recently used memory data in

Authors' addresses: Shengjian Guo, Baidu Security, USA, sjguo@baidu.com; Yueqi Chen, Pennsylvania State University, USA, ychen@ist.psu.edu; Jiyong Yu, University of Illinois at Urbana-Champaign, USA, jiyongy2@illinois.edu; Meng Wu, Ant Group, China, bode.wm@antfin.com; Zhiqiang Zuo, State Key Lab. for Novel Software Technology, Nanjing University, China, zqzuo@nju.edu.cn; Peng Li, Baidu Security, USA, lipeng28@baidu.com; Yueqiang Cheng, Baidu Security, USA, chengyueqiang@baidu.com; Huibo Wang, Baidu Security, USA, wanghuibo01@baidu.com.

This work is licensed under a Creative Commons Attribution 4.0 International License.

© 2020 Copyright held by the owner/author(s).

2475-1421/2020/11-ART147

https://doi.org/10.1145/3428215

$<sup>^{</sup>st}$  These authors contributed equally.

the hierarchical caches for the quick future reuse, thus significantly avoiding latency from visiting memory for the same data. Despite the tremendous importance, CPU cache is prone to cache timing side-channel attacks due to the physically distinguishable timing differences between visiting cache and the memory [Dhem et al. 1998; Gras et al. 2017; Gruss et al. 2016; Kocher 1996; Oren et al. 2015]. Based on the runtime timing statistics of the victims, external adversaries may infer victims' confidential data to certain extents, by exploring the dependency between the confidentiality and the timing characteristics. Practical cache timing attacks [Aldaya et al. 2019; Kocher et al. 2019; Lipp et al. 2018] have been continuously threatening the cybersecurity of computer systems.

The straightforward way to prevent software from timing attacks is to precisely examine the program's cache behavior, thus uncovering the weak sites for leakage mitigation. A broad spectrum of studies have investigated the detection of cache timing side-channel leaks, spanning from static analysis [Doychev et al. 2013; Wang et al. 2019], through symbolic execution [Chattopadhyay et al. 2017; Chu et al. 2016; Wang et al. 2017], to dynamic analysis and testing [Basu et al. 2020; He et al. 2019; Nilizadeh et al. 2019; Xiao et al. 2017].

Nevertheless, the program runtime cache behavior is not only determined by its computation logic but also can be implicitly affected by the microarchitectural factors of hardware. The *out-of-order* execution [Smith and Pleszkun 1985], one of the fundamental optimizations in modern pipelined processors, boosts the pipeline throughput by scheduling proper instructions *out-of-order* rather than in the program order generated by compilers. Although *out-of-order* execution has been designed to be transparent to the programs running atop, it indeed dramatically affects the cache state during program execution.

Recent studies [Bulck et al. 2018; Lipp et al. 2018; Weisse et al. 2018] have revealed that due to the side effects introduced by the *out-of-order* execution to the CPU cache state, sensitive data may leak to external adversaries by deliberately magnifying the effects through cache timing side-channel. To alleviate the leaking risk in secret-critical applications, a systematic leak detection technique for *out-of-order* execution is highly desirable.

The existing program analysis based leak detection approaches mostly focus on the in-order analysis for both sequential software [Chattopadhyay et al. 2017; Coppens et al. 2009; Doychev et al. 2013; Wang et al. 2017, 2019] and concurrent programs [Barthe et al. 2014; Guo et al. 2018]. Recent works also tried modeling the non-functional speculative execution based on abstract interpretation [Wu and Wang 2019], fuzz testing [Oleksenko et al. 2020], and symbolic execution [Guarnieri et al. 2020; Guo et al. 2020; Wang et al. 2020]. Nevertheless, none of them are capable of analyzing the effects of *out-of-order* execution on the program cache state. On the one hand, the in-order methods assume that instruction executions must obey the program order, thus missing the opportunities of reasoning the respective *out-of-order* side effects. On the other hand, the speculative modeling approaches only re-order a bundle of instructions from predicted branches. At the same time, instruction-level *out-of-order* execution [Smith and Pleszkun 1985] may non-deterministically occur everywhere in program execution.

Achieving the goal of accommodating program analysis to *out-of-order* execution has to overcome three significant challenges. The first challenge is about representing the complicated microarchitectural *out-of-order* scenarios in high fidelity, but, inside a user-space analysis software. The second is to enforce the restrictions from both hardware architecture and software semantics in the analysis, to ensure the feasibility of modeled *out-of-order* behaviors. The last is to systematically identify a set of harmful executions, from the vast *out-of-order* search space, that may unveil the violations of specific requirements, e.g., the cache timing leakage-free property; while eliminating a large portion of redundant executions. The blend of these challenges demands new ingredients to program analysis, for studying this emerging spectrum of threats that intensify software flaws in the low-level hardware environment.

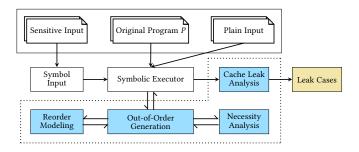

Fig. 1. The overall flow of the SYMO3 method.

Towards this end, we propose SymO<sub>3</sub>, a symbolic execution-based technique for exposing the cache timing leaks coupled with *out-of-order* execution. To address the above challenges, we developed innovative solutions in SymO<sub>3</sub>, as shown by the four components in the dotted area in Fig. 1. First, we break the complicated whole-path *out-of-order* situations into the essential two-event reorder modeling, which can be readily integrated into a stateful symbolic execution to produce *out-of-order* execution of two specific memory instructions. Second, we abstract the hardware and software restrictions into a set of enforceable rules and embed them into the dynamic symbolic executor, to guarantee the correctness of modeled *out-of-order* behavior. Third, we design a new systematic *out-of-order* generation method, which seamlessly incorporates the above two components to select suspicious memory event pairs that may cause leaks from the huge *out-of-order* state space. Finally, we accommodate the constraint-solving based leak analysis into the *out-of-order* scenarios to reason the existence of timing leaks in our SymO<sub>3</sub> framework. To the best of our knowledge, SymO<sub>3</sub> is the first work that tailors symbolic execution for cache timing leakage detection under the context of *out-of-order* execution.

Fig. 1 presents the overall flow of SymO3. Given a program P, which is leakage-free in in-order execution, the sensitive data input, and the non-sensitive plain input, SymO3 symbolizes the sensitive input and ignites the symbolic execution. During the dynamic exploration, the symbolic executor interacts with the *Out-of-order Generation* component which subsequently communicates with the reorder *Necessity Analysis* and the *Reorder Modeling* components, to decide the responsive activities on interpreting memory instructions along an execution path. Based on these new constituents, SymO3 integrates the constraint-solving based leak analysis to perform the timing leak detection under the *out-of-order* scenarios. Finally, SymO3 outputs the identified leak cases.

To conclude, we make the following technical contributions:

- The identification and formalization of cache timing side-channel leaks introduced by the CPU *out-of-order* execution.

- The symbolic execution-based systematic reasoning method, which proposes *out-of-order* generation, reorder modeling, reorder necessity analysis, and leak analysis for identifying harmful *out-of-order* behaviors and inputs that lead to timing leaks.

- The implementation and the evaluation, which demonstrate the effectiveness of the proposed SYMO<sub>3</sub> technique in leak exposure.

We organize the rest of this paper as follows. Section 2 motivates our work, and section 3 states background knowledge. We present the core techniques of  $SymO_3$  in section 4 and the evaluation in section 5. Section 6 discusses the threats to validity, followed by the related work in section 7. Finally, section 8 concludes this paper.

### 2 MOTIVATION

This section uses an example to point out the problem. That is, how *out-of-order* execution can introduce timing leaks into a program, which has no such risks in regular in-order execution.

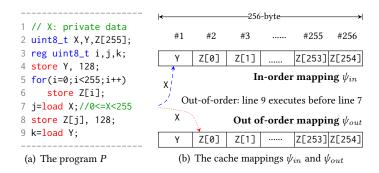

# 2.1 The Running Example

Fig. 2(a) shows the program P. As listed in lines 2-3, P has six variables X, Y, Z, i, j, and k. Both X and Y store 1-byte unsigned integer; Z is a 255-byte array; i, j, and k are register variables. We deem that operating variables X, Y, and Z visits either cache or main memory, while in contrast, accessing register variables i, j, and k requires no memory or cache visit. Moreover, we treat X as the private data of P, and any form of disclosing the value or the range of X from investigating the cache timing information turns to be a side-channel leak.

The load and store operators in P represent memory operations upon the associated operands. For instance, at line 6, the store instruction iteratively writes data to each cell of array Z. At line 7, the load instruction loads the value of X to the register variable j, which is then used in writing Z[j] at line 8. Note that operating i and j involves *register* visits only, and we ignore the side effects because of the negligible timing latency.

For brevity, we incorporate a simplified cache C for the cache behavior analysis. C is a fully-associative cache with the *least recently used* (LRU) replacement policy. This setting means that each local variable in P may associate with arbitrary cache line(s). Moreover, the variable type, the cache availability, and the LRU policy jointly decide the actual cache mappings. We set C to 256 bytes and design each cache line with the exact one-byte capacity. As a result, C has 256 lines in total, and we index them by #n where  $n \in [1, 256]$ .

Fig. 2(b) shows how the variables map to cache C when running P in the in-order and out-of-order manner, respectively. Look into the in-order mapping  $\psi_{in}$  first. Initially, we have an empty cache C. On executing P, the first memory write (line 4) associate cache line #1 with Y. Next, the for loop repeatedly writes array Z 255 times, mapping all array cells to lines #2-#256 of C. This is because each uint8\_t array item uses a whole cache line. Afterward, the load instruction at line 7 reads X. Since cache C has been fully filled, this load would first evict Y from the least recently used cache line #1 and then places X into line #1, as annotated by the dashed arrow in Fig. 2(b). Next, the subsequent write to Z[j] must get a cache hit no matter the value of X since the entire array Z remains in C. Finally, at line 9, reading Y might evict Z[0] or Z[1] because of three points: Y is no longer in the cache; there is no empty cache line in C; the least recently used line could be either line #2 (j!=0) or #3 (j=0) due to the write to Z[j].

This single-path program has a decided cache behavior. The first memory write to Y always triggers a cache cold miss. The following 255 memory writes in the *for* loop consume the rest space of *C*, and they all cause cache cold misses. The next memory read of X incurs a conflict miss while its succeeding write of Z[j] must get a cache hit, as explained above. Finally, loading Y receives a cache conflict miss. This cache behavior shows *P* has no timing leaks in the in-order execution — external observers cannot learn the value of X by the constant program execution timing.

# 2.2 Out-of-Order Execution Brings Timing Leak

As studied above, *P* has stationary cache timing irrespective of the value of X. However, this property could be falsified when taking account of the *out-of-order* execution.

Let us consider a potential *out-of-order* execution case. At line 8, the store to Z[j] has to wait until reading X at line 7 finishes so that j is available in the register. These two instructions are data-dependent and have to execute in-order. By contrast, the subsequent load Y accesses a different address. As a result, under the *out-of-order* execution, once the former two instructions

Fig. 2. Program *P* and the runtime cache mappings.

get stalled due to the cache miss hazard of reading X, the latter load Y could be scheduled. Indeed, such *out-of-order* scheduling is likely to happen. Since Y has been in cache C because of the first memory store at line 4, instruction load Y could be ready for execution in a few processor cycles after querying Y from the cache.

The cache mapping  $\psi_{out}$  at the bottom of Fig. 2(b) shows this *out-of-order* case. Again, cache C is initially empty. The first store to Y and then the array iteration, associate cache blocks #1-#256 with Y and Z. After that, following the *out-of-order* scheduling discussed above, instruction load Y executes and gets a cache hit since Y is still in cache. This hit also updates line #1 to be the *most recently used* line. Hence, cache line #2 turns to be the *least recently used* one now. Therefore, when load X (line 6) executes, it first evicts Z[0] from line #2 by X, as annotated by the dotted arrow in Fig. 2(b). Then, writing Z[j] executes, and P terminates.

Switch to the cache behavior analysis. The first 256 memory writes to Y and Z all have cache cold misses. Then the *out-of-order* execution of load Y results in a cache hit and affects the cache state. The following read of X has to evict Z[0], so it causes a conflict miss. The last memory write of Z[j], however, can lead to two different results: a cache hit if  $X \in [1,255)$ , or a cache miss if X = 0 since Z[0] is no longer in the cache.

Thereby, if an adversary observes that running P costs more CPU cycles, she can learn that X has a high potential to be 0. It is because of the unique cache behavior — only  $X \neq 0$  lets the execution of P have two cache misses, thus distinguishable timing variance — accordingly, *out-of-order* execution brings a new leak.

# 2.3 The Out-of-Order Statistics on Running P

It is worth noting that *out-of-order* execution can take place among various types of instructions. We concentrate on the memory instructions as they directly affect the cache status. Specifically, we only study how the memory *read* operations can be dynamically issued since the memory *write* operations are generally allowed to have in-order executions in practice.

Let us denote the processor reorder buffer has  $\delta$  entries, which indicates at most  $\delta$  consecutive instructions in the program order can enter the reorder buffer at one time, and, may run out-of-order. In other words, if the distance of two reachable instructions, i.e., the number of in-between runtime instructions, is more than  $\delta$ , then the two instructions cannot simultaneously involve in the out-of-order execution. Here we use  $\delta$ =64 for the analysis.

The load Y is the last instruction in *P*. So it may have *out-of-order* behaviors against at most 49 instructions before it. That is, the beginning of the *out-of-order* window for load Y is roughly after store Z[231] in the loop. Note that we treat line 5 as an atomic instruction. Similarly, load

| Scenario      | load X | store Z[j],128 | load Y | Result  |

|---------------|--------|----------------|--------|---------|

| In-order      | miss   | hit            | miss   | no-leak |

| 9∧8           | miss   | hit/miss       | miss   | leak    |

| 9介7           | miss   | hit/miss       | hit    | leak    |

| 9 ← 6         | miss   | hit/miss       | hit    | leak    |

| 7, 6          | miss   | hit            | miss   | no-leak |

| 7, 6, 49      | miss   | hit/miss       | miss   | leak    |

| 9 ~ 6 ~ 7 ~ 6 | miss   | hit/miss       | hit    | leak    |

| 7             | miss   | hit/miss       | hit    | leak    |

Table 1. The cache behaviors of three memory operations under *out-of-order* execution.

X may also expose *out-of-order* behaviors against 49 instructions before it since there is no data dependency between load X and its predecessors.

Though program P has only two memory read instructions, the number of distinct *out-of-order* behaviors based on these two load operations may explode to approximately 49\*49=2,401 cases. Moreover, we group these cases into seven equivalent classes w.r.t reading X and Y, and writing Z[j], as shown in Table 1.

Table 1 summarizes the possible *out-of-order* execution scenarios and the resulting cache behaviors. Operator  $\curvearrowright$  means its left-side operand executes before the right-side operand, thus forming an *out-of-order* situation. For example,  $9 \curvearrowright 8$  indicates line 9 executes right before line 8, while  $9 \curvearrowright 6$  implies line 9 executes before some store Z[i] instructions in the loop.  $7 \curvearrowright 6 \curvearrowright 9$  shows that line 7 executes before some store Z[i] at line 6, and line 9 runs right after the loop;  $7 \curvearrowright 6 \curvearrowright 9 \curvearrowright 6$  depicts both line 7 and line 9 runs before some store Z[i], but line 7 has to run before line 9.

In Table 1, not all *out-of-order* cases are harmful, and  $7 \curvearrowright 6$  is the harmless case. However, a high portion (6/7) of *out-of-order* scenarios could introduce leaks. Interestingly, the appearances of leaks differ. For example, in the case of X=0, only  $9 \curvearrowright 8$  and  $7 \curvearrowright 6 \curvearrowright 9$  would have all-miss situations, thus obviously longer timing. Moreover, if X!=0, these two have the same timing to the in-order execution of P, thus no visible leaks. By comparison, if X!=0, the other four groups would get two-hit results and faster timing, while upon X=0, the timing equals the in-order execution timing.

To conclude, the subtle timing leaks in *P* arise from the simultaneous blend of proper *out-of-order* schedules and specific secret inputs. To this end, a systematic analysis technique that (1) automatically distinguishes feasible leak-introducing *out-of-order* schedules, and (2) precisely generates the leak-endorsing inputs would be indispensable. However, this analysis has rarely been achievable in literature, and such shortage motivates our SymO<sub>3</sub> work.

#### 3 PRELIMINARIES

This section presents the preliminary knowledge of our work.

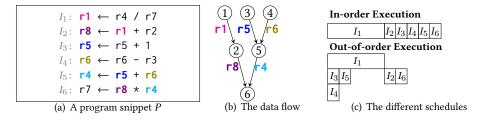

Fig. 3. High-level view of the program execution.

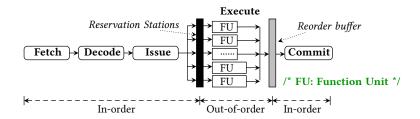

Fig. 4. Microarchitectural view of the instruction execution.

### 3.1 The Out-of-Order Execution

3.1.1 The Concept. Pipelined processors usually divide the execution of instruction into several stages to utilize the pipelines for best throughput. However, it is believed that a deeper pipeline will not contribute more beyond some turning points due to the hardware cost and the control/data hazards. Alternatively, the instruction-level parallelism, especially the *out-of-order* execution, plays a crucial role in promoting the pipeline performance [Li et al. 2004].

At the high-level, *out-of-order* execution leverages the dynamic data flow rather than the static program order to schedule instructions. A processor usually maintains a "sliding window" of consecutive instructions. Once an instruction turns to be ready, the processor selects that instruction from the window and schedules it to run. Therefore, the executed orders of independent instructions may disobey the original program order.

Fig. 3 shows an example program P [Etsion 2013] as well as the *in-order* and *out-of-order* instruction scheduling strategies on running P. Fig. 3(a) lists the six instructions of P, labelled by  $I_n$  where  $n \in [1,6]$ . Fig. 3(b) presents the data flow graph in which a node corresponds to an instruction, and the directed edges denote the data dependencies. For example, the edge from node ① to ② indicates instruction  $I_2$  depends on  $I_1$ , in terms of the annotated r1. Fig. 3(c) draws the two schedulings of these instructions on running P.

Under the *in-order* execution, instructions are sequentially executed in the program order (ref. Fig. 3(c)). Though  $I_3$ ,  $I_4$ , and  $I_5$  are data-independent of preceding instructions  $I_1$  and  $I_2$  (ref. Fig. 3(b)), they cannot execute before these predecessors.

Instead, out-of-order execution exploits the parallelism of scheduling independent instructions. Assuming division computation consumes 20+ cycles while others like addition and subtraction merely need 1-3 cycles. Then the first instruction  $I_1$  would cost an inevitably long execution time. However, during such long latency, processors can schedule  $I_3$ - $I_5$  to run ahead of  $I_2$  (ref. Fig. 3(c)). Though  $I_5$  relies on both  $I_3$  and  $I_4$ , and it has to execute after them, this schedule still benefits the overall performance. Note that out-of-order execution must preserve the program dependency semantics. Hence,  $I_2$  and  $I_6$  cannot be scheduled beforehand.

At the microarchitectural level, the instruction execution process can be divided into multiple steps as *fetch*, *decode*, *issue*, *execute*, and *commit*, as shown in Fig. 4 [Etsion 2013]. Following the program order, a processor fetches and decodes a set of instructions and issues them to multiple reservation stations (RSs). Once the operand data of an instruction gets ready and no contention appears on the available executing resource, i.e., a specific function unit (FU), the instruction will be moved from the RS to that FU to run. This mechanism, thus, gives birth to *out-of-order* execution in a first-ready-first-run manner. At the end of the *execute* step, finished instructions broadcast their computed data to signal the awaiting dependents to proceed. Finally, the finished instructions enter the circular *reorder buffer* and commit in the program order again.

3.1.2 Our Focus. In this work our SymO $_3$  method leverages symbolic execution to examine the cache side-effects from the *out-of-order* execution of memory instructions. Two recent symbolic execution methods SpecuSym [Guo et al. 2020] and KLEESpectre [Wang et al. 2020] model microarchitectural speculative execution for side-channel leak pinpointing and vulnerability detection, which closely relate to SymO $_3$ . However, SymO $_3$  has threefold distinctions.

The speculative execution studied in [Guo et al. 2020; Wang et al. 2020] and the out-of-order execution studied in SymO<sub>3</sub> are two special instances of the general out-of-order execution, as later discussed in Section 6. To minimize the vagueness, we by default use the term out-of-order execution throughout this paper to refer to the out-of-order scenario studied in SymO<sub>3</sub>. Speculative execution beforehand probes a sequence of instructions under a predicted branch leg, while out-of-order execution tries to schedule the ready instructions as soon as possible to the reservation stations. From the microarchitectural angle, they have orthogonal semantics; thus, we composite the cache impacts from both in Section 5.4.

Besides, in Section 4, we establish the formalization and algorithm for the *out-of-order execution*. They highly differ from those in SpecuSym and KLEESpectre, despite all these methods share the fundamental state-forking mechanism from KLEE. Also, SpecuSym and KLEESpectre developed forward modeling techniques while in contrast, SymO<sub>3</sub> relies on backward modeling and prunes unnecessary forward executions. However, SymO<sub>3</sub> cannot model the speculative behaviors in SpecuSym and KLEESpectre, and vice versa.

Moreover, SymO<sub>3</sub> broadens the spectrum of the dynamic partial order reduction (DPOR) style analysis to the cache analysis in Section 4. Classic DPOR methods like [Flanagan and Godefroid 2005; Yang et al. 2008] are confined to the equivalent classes of thread interleavings. SymO<sub>3</sub> fuses the hardware behaviors and the software restrictions into a synergistic reasoning algorithm upon symbolic execution. Its general *out-of-order* modeling approach may apply to analogical problems, e.g, the relaxed memory model analysis [Kusano and Wang 2017] with tolerable porting efforts.

#### 3.2 The Cache Basics

CPU cache dedicates to reducing the average latency of visiting memory locations from the CPU. When the CPU requests a memory operation for some data, it first inquiries the data existence in the cache. If not cached, which indicates a cache miss, the request goes to memory to load data into cache, and then returns the data to CPU. If the data is in the cache, which turns to be a cache hit, the request directly retrieves the data without touching the memory.

The modern cache hierarchy often consists of L1, L2, and L3 caches. L1 cache has two sub-types as instruction cache (i-cache) and data cache (d-cache). L1 and L2 caches reside in the same processor core, while L3 cache is shared among multiple cores. In general, the closer to the processor core, the faster cache speed and the smaller cache capacity, and vice versa. For example, the Intel *Coffee Lake* microarchitecture-based CPU Core i7-8850H has six cores that share a 9MB L3 cache. Meanwhile, each core owns 64KB L1 cache (half i-cache and half d-cache) and 256KB L2 cache.

Program analysis-based cache analysis methods [Basu and Chattopadhyay 2017; Brotzman et al. 2019; Chattopadhyay et al. 2017; Guarnieri et al. 2020; Guo et al. 2018, 2020; Gysi et al. 2019; Wang et al. 2020, 2017, 2019; Wu and Wang 2019] abstract the microarchitectural behaviors of certain instructions to form interceptable models, e.g., the cache-state abstract domain and the constraint formula of cache behaviors, for the reasoning upon software-level techniques. However, modeling the complete cache hierarchy by program analysis yet misses practical solutions. First, the consistency synchronization within the hierarchical caches can rapidly deteriorate the state expolsion problem of cache status. Second, latencies of different caches pose extraordinary challenges for the uniform and precise modeling of timing problems. Third, the L3 cache shared by multiple cores largely exaggerates the above two issues. To the best of our knowledge, only one

Fig. 5. The tag id, associated set and line offset of addr under a 32KB 8-way cache.

recent static analysis method [Gysi et al. 2019] covers L2 and L3 caches of a fully-associative cache. However, the cost of modeling mainstream set-associative caches remains unknown. Moreover, the *out-of-order* analysis for timing leak detection still lacks, even under the L1 cache. As a result, in this work we concentrate on the L1 d-cache and use it to represent the cache for short.

In practice, the cached data is organized by cache lines and cache sets. For instance, the 64-byte cache line size of a 32KB d-cache means there are 512 (32KB/64B) lines in total. The 64-byte size also implies the minimum unit of contiguous data that loads from memory each time. The approaches that associate different memory locations to certain cache lines leads to three major cache types as direct-mapped cache, fully-associative cache, and set-associative cache. In our experiments, we evaluate SymO<sub>3</sub> on set-associative caches because of its proven practicability.

In accordance with the latter cache analysis in Section 4.5, we define some formal notations:

- *addr* represents the memory address involved in a memory operation instruction.

- set(addr) gives the cache set with which addr associates.

- tag(addr) gives the tag id of addr w.r.t a given set-associative cache.

- K denotes the cache associativity, e.g., a 8-way set-associative cache indicates each set contains eight cache lines thus K=8.

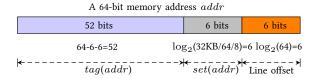

Fig. 5 demonstrates the calculations of the tag id and the associated set of a 64-bit memory address addr under a 32KB 8-way set-associative cache. We assume each cache line here has a 64-byte size. Due to this 64-byte line, the rightmost 6 bits, which represent the location of the 1-byte data of addr in a mapped cache line, can be calculated by  $\log_2(64)=6$ . Next, based on the 8-way associativity and the 64-byte line size, we compute the number of cache sets to be 32KB/64/8=64. Thus set(addr) returns the value of the middle 6 bits. Then, the remaining 52 bits belong to the tag id, which can be obtained by tag(addr).

Then, we define a function  $\phi$  to formally check whether two addresses  $addr_1$  and  $addr_2$  could map to the same cache line:

$$\phi\left(addr_1, addr_2\right) := set(addr_1) = set(addr_2) \land tag(addr_1) = tag(addr_2) \tag{1}$$

Note that  $\phi$  does not require  $addr_1$  and  $addr_2$  to be the same address. Exampling the Fig. 5 cache, visiting  $addr_1$  could load a block of 64-byte memory data d to fully fill a cache line l. If d still exists in l on visiting  $addr_2$  afterward and  $\phi$  satisfies, a cache hit appears.

## 3.3 The Cache Timing Leaks

Confidential data of critical programs may potentially leak to the unsafe zone via microarchitectural side-channels when executing the vulnerable program implementations. The indistinguishability property [Yu et al. 2019] formalized the elimination of a microarchitectural side-channel. That is, for any public input t and any two secret inputs  $\tau$  and  $\tau'$ , their execution traces must have no distinguishable physical effects against a specific microarchitecture component:

$$\psi := \forall t, \tau, \tau' . Obs \left( Imp_{\mu}(P(t, \tau)) = Obs \left( Imp_{\mu}(P(t, \tau')) \right) \right)$$

(2)

Equation (2) characterizes the general abstraction of the side-channel-free property. Function Obs evaluates the external adversary's observation ability on the physical effects.  $Imp_{\mu}$  represents a microarchitecture implementation. P is the running program that inputs both public and secret data, e.g., an encryption algorithm program that processes the plaintext and a private key to generate the ciphertext.

Projecting the  $Imp_{\mu}$  to the cache, we obtain the leakage-free property of cache timing sidechannel as follows. The cache timing leaks stem from the timing variance of cache behaviors when executing different inputs. If we treat program P as a function of input  $in := (t, \tau)$ , and let  $T(P(t, \tau))$ denotes the execution time of an execution trace on in, then the observation Obs against cache timing can be approximated to the observed execution time of that trace upon input in:

$$\forall t, \tau : Obs (Imp_{u}(P(t,\tau)) \approx \forall t, \tau : Obs_{timing}(P(t,\tau))$$

(3)

*P* may have multiple traces from various program paths. Since we target timing leaks introduced by *out-of-order* execution, we assume *P* is leakage-free under *in-order* execution, which is:

$$\psi_{in\ order} := \forall t, \tau, \tau' \ . \ Obs_{timina}(P(t,\tau)) = Obs_{timina}(P(t,\tau'))$$

(4)

Still,  $\tau$  and  $\tau'$  represent any pair of secrets, and t is the public input. P is free of cache timing side-channel leakage if two arbitrary *in-order* program traces have indistinguishable execution time. Similarly, we define whether P suffers from new leakage under *out-of-order* execution by checking the following formula:

$$\psi_{out\_order} := \psi_{in\_order} \land \Big(\exists t, \tau, \tau' \ . \ Obs_{timing}(P_{out\_order}(t, \tau)) \neq Obs_{timing}(P_{out\_order}(t, \tau'))\Big)$$

(5)

A new leak appears under the *out-of-order* execution context if two secret inputs  $\tau$  and  $\tau'$  do exist and cause distinguishable  $Obs_{timing}$  in the corresponding *out-of-order* traces. Note that we primarily care about whether the secret can interfere with the cache state along an *out-of-order* trace. In the analysis, we configure t to a concrete value to reduce the runtime overhead.

# 3.4 The Threat Model

As manifested in Section 2.2, external adversaries may learn the private data from analyzing the victim's runtime timing under *out-of-order* execution. To be capable of accomplishing such a threat, the adversaries need to have privileged access to a malicious process sharing the physical cache with the victim; so those adversaries can measure the interested memory access latency through probe methods [Gruss et al. 2016; Yarom and Falkner 2014; Zhang et al. 2011]. They should also be able to reason about the source code of the victim for possible *out-of-order* leaks as well as triggering the execution of the victim. We believe this threat model is reasonable as it has been proved feasible in practical attacks, such as [Disselkoen et al. 2017; Osvik et al. 2006; Yarom and Falkner 2014]. It is also widely adopted in recent side-channel reasoning works [Brotzman et al. 2019; Doychev and Köpf 2017; Guo et al. 2020; Wang et al. 2020, 2017; Wichelmann et al. 2018].

#### 4 OUT-OF-ORDER SYMBOLIC EXECUTION

This section reviews the baseline symbolic execution and then introduces the core components of our SymO<sub>3</sub> which build upon the baseline algorithm.

# 4.1 The Baseline Symbolic Execution

Symbolic execution [Clarke 1976; King 1976] has witnessed extensive advances [Bergan et al. 2014; Bucur et al. 2011; Cadar et al. 2008; Ciortea et al. 2009; Guo et al. 2015; Pasareanu and Rungta

2010; Poeplau and Francillon 2020] in recent years. In this work, we adopt the recursive symbolic execution algorithm and related knowledge from [Guo et al. 2015, 2018] as the baseline upon which we build the new components of  $SymO_3$ .

First, we assume that a program P comprises a finite set of paths, and each path contains a finite sequence of instructions. Let inst be short for an instruction then  $\epsilon := \langle l, inst, l', nxt \rangle$  denotes the symbolic event of an inst. l and l' represents the program locations before and after inst, and nxt points to the next symbolic event for execution. The execution of P on input  $in:=\{t,\tau\}$  explores a series of symbolic events along the program path to which in leads.

Second, a symbolic state s stands for the frontier of exploring a path in P during the dynamic execution. We also present s in a tuple as  $s:=\langle \epsilon, pcon, \hat{m} \rangle$ .  $\epsilon$  is the current symbolic event to execute at s; pcon is the path condition from the execution entry to s;  $\hat{m}$  contains the memory mappings of variables and their symbolic values at the time reaching  $\epsilon$ .

Third, we abstract away the implementation details of symbolic event interpretation and perform our analysis only against the execution of memory events. A memory event must associate with a memory operation instruction, i.e., a memory *read* like v=load addr, or a memory *write* as store addr val, where *addr* is a memory address, and val denotes a symbolic value. We use M-event to refer to this event type. Other kinds of symbolic events, such as branch event and arithmetic events, would execute as usual in symbolic execution since they do not directly impact the cache status.

## 4.2 The Out-of-Order Generation

# Algorithm 1 The Out-of-Order Generation Algorithm

```

1: Initially: Create a global stack ST; start STDSYMEXEC with a seed state s_0 on input \{t_0, \tau_0\}.

2: procedure StdSymExec (Symbolic_State state)

ST.push(state);

3:

if state.\epsilon is a M-event then

▶ The memory event interpretation

4:

▶ The entry of new SYMO<sub>3</sub> analysis

O<sub>3</sub>GEN(state);

5:

StdSymExec(NextSymState (state));

6:

else

7:

STDSYMEXEC(NextSymState\ (state));

▶ Other events execute as usual

8:

end if

9.

ST.pop();

10:

end procedure

11:

12:

13: function O<sub>3</sub>GEN (Symbolic_State crt)

crt.done \leftarrow crt.done \cup crt.\epsilon:

14:

if crt.\epsilon is a memory read event then

15:

Let e be the closest event in crt.trace that RNA(crt, e) returns true; \rightarrow RNA analysis

16:

if e \neq null then

17:

18:

prv \leftarrow the symbolic state that was about to execute e;

if crt.\epsilon \notin prv.done then

19:

▶ Invoke the out-of-order modeling

ReorderModeling (crt, prv);

20:

end if

21:

end if

22:

end if

23:

24:

crt.trace \leftarrow crt.trace \cdot crt.\epsilon;

25: end function

```

In this section, we introduce the main procedure of SymO<sub>3</sub> which starts at the interpretation point of a M-event. We observe that, fundamentally, the feasible *out-of-order* behaviors among a window of instructions can be decomposed to the blend of multiple two-instruction reorderings. However, a straightforward reordering enumeration of potential instruction pairs can quickly result in the state explosion. Also, certain rules of the environmental restrictions should be applied to ensure the feasibility of the various reorderings. Moreover, a large portion of these pairs might be redundant in terms of the unchanged cache state. Inspired by the *dynamic partial order reduction* [Flanagan and Godefroid 2005; Yang et al. 2008, 2010], which searches for equivalent classes of thread interleavings in concurrency analysis, we design a new algorithm *Out-of-order Generation*, to systematically generate unique *out-of-order* symbolic states for the cache analysis.

4.2.1 The Algorithm. Algorithm 1 presents the proposed algorithm, which builds upon the baseline symbolic execution procedure StdsymExec. We retain the unchaned part of StdsymExec, e.g, the handling of other symbolic events except the memory events, and the sub-procedure NextSymState which processes a symbolic event and returns the new state. Details of StdsymExec can be found in [Guo et al. 2015, 2018]. The main changes start at line 5 — a new function O<sub>3</sub>Gen which ignites the generation of instruction-level out-of-order executions by a backward analysis against the current state state.

To keep pace with  $O_3GEN$ , we extend the symbolic state s to be  $s:=\langle \epsilon, pcon, \hat{m}, trace, done \rangle$ . During the exploration of s, trace records the executed memory events; done records the set of scheduled events at s, since the out-of-order modeling now may schedule multiple events at the same program location. Generally,  $O_3GEN$  first updates the done set of state crt (line 14), meaning that event  $crt.\epsilon$  has been processed in this backtracking, to avoid future re-analysis. Then, if  $crt.\epsilon$  is a memory read event,  $O_3GEN$  backwardly searches crt.trace for the closest event e that may run out-of-order with  $crt.\epsilon$ , and the  $Reorder\ Necessity\ Analysis\ (RNA, ref.\ Section 4.3)\ can return <math>true$  (line 16). If such e does not exist,  $O_3GEN\ appends\ crt.\epsilon$  to  $crt.trace\ (line\ 24)\ and\ exits.$

In contrast, if the desired event e does exist, then at line 18, O<sub>3</sub>GEN retrieves a prior symbolic state prv who was about to execute e. More importantly, if  $crt.\epsilon$  is not in the done set of state prv, O<sub>3</sub>GEN sends crt and e to function ReorderModeling for the two-event out-of-order behavior modeling (ref. Section 4.4). In the end, O<sub>3</sub>GEN also updates crt.trace at line 24.

## Assumptions:

b only depends on a d only depends on c c is independent of a and b Reorder buffer size: 3 Cache type: fully-associative

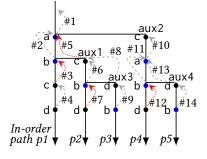

Fig. 6. The out-of-order generation and the preserved four new states

4.2.2 The Example. Fig. 6 shows an example for Algorithm 1. Without out-of-order execution, there is an *in-order* execution path p1 of four memory read events a, b, c, and d. We assume that b only depends on a and d only depends on c; but, c is independent of both a and b. Then, the example is to, under the given assumptions, systematically generate new symbolic states to model the distinct out-of-order behaviors along with exploring the *in-order* path p1.

Following Algorithm 1, the forward symbolic execution procedure STDSYMEXEC calls the first  $O_3$ Gen, marked as #1, on approaching event a. Here we use the *path-event* convention, to name a symbolic state. So the state right before a is p1-a. The  $O_3$ Gen #1 puts a into the p1-a.done, but it cannot find an event e before a because of the empty e1-a.trace. So #1 quickly returns after placing a into e1-a.trace.

Whereafter, the second  $O_3$ GEN invocation, #2, starts on arriving b. As b relies on a, the RNA judges *false* (line 16, Algorithm 1), which means b cannot run before a. We color the backward arrow in gray to mark such infeasible reordering. Similarly, both *p1-b.trace* and *p1-b.done* now contains b after #2.

Going to c,  $O_3$ GEN #3 finds that c and the closest event b qualify the RNA rules (ref. Algorithm 2). First, the in-between distance, *one*, is less than the *reorder buffer size* of *three*. Second, b and c are data-independent; thus, they are unreachable in the data dependency graph built from a, b, and c. Third, due to the assumed fully-associative cache, b and c have a mutual effect against the cache state. Lastly, c is not in the *done* set of p1-b who only contains b. As a result, the REORDERMODELING function (line 20, Algorithm 1) forks a new state aux1 from p1-b, reorders c and b, and places aux1 to the global state pool for future exploration.

Proceeding to d,  $O_3$ GEN #4 also returns early due to the assumed dependency between c and d. After the execution goes to the end of p1, STDSYMEXEC pops out states p1-d, p1-c, and p1-b due to the recursion, and uses aux1 for the new exploration. At this point, aux1 is to execute c.  $O_3$ GEN #5 duplicates a new state aux2 from aux1, to model the *out-of-order* situation between c and a. After #5, STDSYMEXEC schedules c and continues to b. Again,  $O_3$ GEN tries backtracking from b to c (#6). Though this time #6 can get through the RNA rules, it fails the checking at line 19 of Algorithm 1 because aux1.*done* already contains b from inheriting the *done* set of p1-b. Thereby, the condition  $b \notin aux1$ .*done* is unsatisfiable, and #6 cannot trigger ReorderModeling for this reason.

Repeating StdSymExec until the global state stack St gets empty, our *Out-of-order Generation* algorithm systematically explores unique *out-of-order* event pairs and prunes infeasible executions. Moreover, it integrates the new auxiliary states into symbolic executor in a uniform way. In the result of Fig. 6, our algorithm backtracks *fourteen* times but only preserves *four* distinct states that represent unique *out-of-order* behaviors, as shown by the dotted arrow lines in Fig. 6.

*4.2.3 The Proof.* To show that Algorithm 1, when combined with Algorithm 3 and 2, covers all feasible *out-of-order* program executions, we prove the following theorem based on induction:

Theorem 4.1. Suppose an in-order execution of a program with m instructions generates an event sequence  $\{e_1, e_2, ..., e_m\}$ . Algorithm 1 generates the corresponding event sequences for any valid out-of-order execution of the program.

Consider the first *n* instructions (in program order):

- (1) When n=1, Theorem 4.1 holds because one event only has one event sequence, regardless of in-order or out-of-order.

- (2) Assume Theorem 4.1 holds for the first n instructions; we denote all possible event sequences as  $P_1, P_2, ..., P_{X_n}$ .  $X_n$  represents the total number of valid executions, including both in-order and out-of-order.

- (3) When considering the first n+1 instructions, we first notice that any valid event sequence can be only constructed by inserting  $e_{n+1}$  to an event sequence P from  $P_1, P_2, ..., P_{X_n}$  without interchanging the order of any two events in the original sequence P, modulo the constraints specified in Algorithm 2. The proof is straightforward: since  $e_{n+1}$  is younger than  $e_1, e_2, ..., e_n$  in program order, its execution won't affect the execution of the prior n instructions. Therefore,

- in any valid execution event sequence of the first n + 1 instructions, subtracting  $e_{n+1}$  should yield a valid event sequence of the first n instructions which appears in  $\{P_1, P_2, ..., P_{X_n}\}$ .

- (4) To construct all possible execution sequences consisting of  $e_1, e_2, ..., e_{n+1}$ , we start by appending  $e_{n+1}$  to every sequence  $P \in \{P_1, P_2, ..., P_{X_n}\}$ , and do  $O_3$ GEN on the final state of P for  $e_{n+1}$  based on Algorithm 1.  $O_3$ GEN swaps the  $e_{n+1}$  with the previous event along the sequence P unless the *distance* or *data dependency* constraint check in Algorithm 2 fails. This ensures that we cover all possible event sequence based on P, since  $e_{n+1}$  cannot be moved forward due to the RNA rules, and doing  $O_3$ GEN for all possible sequences with n instructions  $(e_1, e_2, ..., e_n)$  is sufficient due to the analysis in (2).

# 4.3 The Reorder Necessity Analysis

```

Algorithm 2 The Reorder Necessity Analysis (RNA)

1: function RNA (Symbolic State crt, Event e)

d \leftarrow the distance between crt.\epsilon and e in the program order;

if d > 0 \&\& d < \text{rbs then}

The distance check

3:

G \leftarrow the data dependency graph of crt.trace;

4:

if crt.\epsilon and e are unreachable in G then

▶ The dependency check

if crt.\epsilon and e have mutual cache effects then

▶ The cache effect check

6:

return true;

end if

8:

end if

end if

return false;

12: end function

```

This section proposes the *Reorder Necessity Analysis* (RNA), to assist the above *Out-of-order Generation* algorithm. Due to the microarchitectural restrictions and the software data dependency, only a subset of memory instructions may get involved in *out-of-order* execution. Therefore, we design Algorithm 2 to enforce the necessity analysis against two candidate events.

In general, Algorithm 2 conducts a threefold analysis. The primary function RNA takes a symbolic state crt and a symbolic event e as inputs. At line 2, RNA first calculates the distance d — the number of events between e to  $crt.\epsilon$  in the program order.

Then, if  $d \notin (0,rbs)$ , RNA directly returns false at line 11, meaning that out-of-order execution of  $crt.\epsilon$  and e is infeasible. Otherwise, RNA continues to data dependency analysis (lines 4-5). Here rbs shorts for the processor reorder buffer size. Learned from Fig. 4, instructions enter and leave the reorder buffer in the program order. Only the head instruction in this circular buffer has retired can its direct successor become the head. Then an awaiting instruction can enter this buffer. Thus, if the number of in-between events of  $crt.\epsilon$  and e reaches or exceeds rbs, the two events have no chance to perform the out-of-order execution.

Going to the data dependency analysis, at line 4 RNA constructs a data dependency graph from crt.trace. Note that based on symbolic execution, we can obtain dynamic variable values to build a precise graph of G like Fig. 3(b). If two events, i.e.,  $crt.\epsilon$  and e, cannot reach each other in the directed graph G, we affirm that they are independent and proceed to the third analysis, which checks cache state interference. Otherwise, RNA also returns false.

The last analysis checks the mutual effect on the cache state between the given events (lines 6-7). The inversed execution of two independent events may not necessarily be useful if the cache state,

e.g., the cache content or the most recently used line of a cache set, remains the same no matter which event runs first. If events e and  $crt.\epsilon$  cannot impact each other regarding the cache status, RNA returns false. If not, we deem the necessity of out-of-order modeling and let RNA return true.

We use Fig. 7, which depicts the *out-of-order* scenario of the motivating example, to explain Algorithm 2. First, by observing the in-order events on the right-side in-order trace, we count the distance between two events load X and load Y be *two* (including the former). Thus,  $d \in (0,rbs)$  satisfies because rbs assumes to be 64 in the example. Second, since X and Y are not aliasing, the memory read events of them are data-independent. Third, recall that the motivating example uses a fully-associative cache. We view such a cache as a particular single-set cache to which any memory operation might cause status change. Consequently, it is necessary to reorder the two events, and RNA correspondingly returns true.

Note that the analysis under fully-associative cache costs more computations but misses no suspicious cases. Moreover, for regular set-associative caches, memory events associated with different sets may get RNA to return false.

# 4.4 The Reorder Modeling

As discussed, the complicated *out-of-order* execution along a program path can essentially break into the combination of multiple two-event cases. We design the basic reorder modeling method of two given events in Algorithm 3, which can embed into the *Out-of-order Generation* algorithm introduced in Section 4.2.

Function ReorderModeling inputs two symbolic states, crt and prv, and tries to schedule them out-of-order, which is to let event  $crt.\epsilon$  run before  $prv.\epsilon$ . Note that crt must be forwardly reachable from prv, and event  $crt.\epsilon$  has to be independent of  $prv.\epsilon$ . Otherwise,  $crt.\epsilon$  cannot execute beforehand.

# Algorithm 3 The Reorder Modeling of Two Symbolic Events.

```

1: function ReorderModeling (Symbolic_State crt, Symbolic_State prv)

aux \leftarrow fork a new symbolic state from prv and put it to state pool;

e \leftarrow declare an event variable that points to aux.\epsilon;

3:

q_1, q_2 \leftarrow declare two empty queues for symbolic events;

4:

while e \leq crt.\epsilon do

5:

if e is dependent of aux.\epsilon then

6:

q_1.back().nxt = e;

7:

q_1.push(e);

8:

else

9:

q_2.back().nxt = e;

10:

q_2.push(e);

11:

e \leftarrow the next event along the execution path to crt;

13:

end while

aux.\epsilon \leftarrow q_2.\text{front()};

▶ Update the current event of aux

15:

q_2.back().nxt = q_1.front();

▶ Concatenate two event lists

16:

q_1.\text{back}().nxt = crt.\epsilon.nxt;

Redirect to the next event

Clean temporary queues q_1 and q_2;

19: end function

```

At the beginning, Reorder Modeling forks a new auxiliary state aux from its second input prv (line 4), to act as the modeling transmitter. After the duplication, aux has the same state snapshot to prv. Then, at lines 3-4, we define a temporary symbolic event e that points to  $aux.\epsilon$ , and two empty queues  $q_1$  and  $q_2$ . Next, ReorderModeling iteratively checks the dependency of e and  $aux.\epsilon$  (line 6), and updates e to the next event (lines 13) along the trajectory between prv and crt, until e reaches  $crt.\epsilon$  at the trajectory tail (line 5).

The while loop (lines 5-14) separates the iterated events into two queues. If the event that e references to is data-dependent of  $aux.\epsilon$  (line 6), we placed it to  $q_1$  (line 8). Similarly, we put events that are irrelevant to  $aux.\epsilon$  into  $q_2$  (line 11). Besides, before pushing e to either  $q_1$  or  $q_2$ , we link the neighboring events by associating the queue tail event with e (lines 7 and 10).

After the loop, ReorderModeling performs three updates. First, it resets  $aux.\epsilon$  to the head event of  $q_2$  (line 15), indicating that aux now is to execute the first event of the linked events that are irrelevant to the original  $aux.\epsilon$ . Second, it makes  $q_2$ 's tail event point to  $q_1$ 's head event (line 16) to reconnect the two event sequences. Finally, it sets the successor of  $q_1$ 's rear event to the next event of  $crt.\epsilon$  (line 17), to finish rebuilding the event chain between aux and crt. In the future, once the symbolic executor schedules state aux, it would execute along the reconstructed event chain from aux to crt, which realizes the artificial out-of-order behavior.

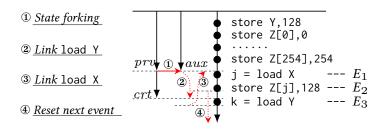

Fig. 7. Out-of-order modeling of events  $E_1$  and  $E_3$

In general, ReorderModeling mimics the two-event *out-of-order* execution by exploiting the stateful instinct of symbolic execution. Fig. 7 shows the modeling of the studied case in Section 2.2. To schedule load Y before load X, let us name the two load events to be  $E_1$  and  $E_3$ , respectively. Following Algorithm 3, we divide the modeling progress into four steps in Fig. 7. The motivating program P has only one path; thus, we depict the path by a sequence of memory instructions. The black nodes represent the corresponding memory events.

In the example, we assume that the invocation of Reorder-Modeling happens at state crt, who is about to execute  $E_3$ . The other state, prv, was to execute  $E_1$ . Since crt is forwardly reachable from prv and  $E_1$  and  $E_1$  are data-independent, Reorder-Modeling can start with the two states prv and crt safely.

As shown in Fig. 7, step ① first creates aux, a duplicate of state prv. Now,  $aux.\epsilon$  is  $E_1$ . After the while loop in ReorderModeling , we get  $q_1 := [E_2, E_1]$  and  $q_2 := [E_1]$ . Next, step ② resets  $aux.\epsilon$  to the front event of  $q_2$ , which turns to be  $E_1$ . Later, step ③ makes the nxt event of  $E_1$  be  $E_1$  because  $E_1$  is the head event in  $q_1$ , and  $E_1$  is also the back event of  $q_2$ . Finally, step ④ redirects the successor of  $q_1$ 's tail event,  $E_1$ , to be the nxt event of  $crt.\epsilon$ , which goes to the end of the path. So far, the event chain reorganization finishes. In the future, the symbolic executor would first steer aux to  $E_1$  and produce the out-of-order behavior accordingly.

# 4.5 Cache Leak Analysis

This section leverages the constraint-solving based approach to reason about the existence of leaks. Specifically, we adopt the per trace approach [Basu and Chattopadhyay 2017; Chattopadhyay 2017;

Chattopadhyay et al. 2017; Guo et al. 2018, 2020; Wang et al. 2020], to conduct leak analysis against the memory events on each *out-of-order* execution trace.

# Algorithm 4 The Cache Leak Analysis

```

1: procedure StdSymExec (Symbolic_State state)

2:

if state.\epsilon is a M-event then

3:

CACHELEAKANALYSIS(state);

▶ Start the leak analysis

4:

O<sub>3</sub>GEN(state);

5:

6:

7:

end if

9: end procedure

10:

11: function CacheLeakAnalysis (Symbolic_State crt)

if crt is an out-of-order state && crt.\epsilon is relevant to sensitive input then

12:

13.

\sigma \leftarrow form the leak constraint for event crt.\epsilon;

Solve \sigma \wedge crt.pcon for satisfiable inputs;

14:

15:

end if

16: end function

```

Algorithm 4 describes the leak analysis. Generally, before starting the  $O_3$ Gen on a memory event  $state.\epsilon$ , we check whether it may lead to a cache timing leak. That is, before symbolically executing  $state.\epsilon$ , we analyze if, under some specific inputs, the cache behavior of  $state.\epsilon$  differs from its original behavior under in-order execution. SymO $_3$  accomplishes such functionality by adding Cacheleakanalysis into the StdsymExec (line 4). In this new function, if the state crt is generated from the out-of-order modeling, and  $crt.\epsilon$  is relevant to the sensitive input (line 12), we build the constraint  $\sigma$  that describes the leak condition of  $crt.\epsilon$  (line 13), and solve  $\sigma \land pcon$  for possible solutions (line 14).

Recall that we assume the target program is timing leakage-free in in-order execution; thus, each in-order memory event causes either must-hit or must-miss. Then,  $\sigma$  states the condition for the existence of a different cache behavior:

$$\sigma := \exists in. (\alpha_{in}(e_i) \neq \Delta_{e_i}) \tag{6}$$

To be specific, given a memory event  $e_i$ , if there exists an input in that makes  $\alpha_{in}(e_i)$ , the cache hit constraint of  $e_i$  under *out-of-order* execution, compute a different value from the in-order cache behavior  $\Delta_{e_i}$ , then there is a leak at  $e_i$ . Here  $\Delta_{e_i}$  is a constant hit/miss value, e.g., 1 for hit and 0 for the miss, that can be obtained by an *in-order* run with arbitrary input.

To formally present  $\alpha_{in}(e_i)$ , we need two more notations:

- The *trace* constituent of a symbolic state consists of the executed memory events  $\{e_1, ..., e_n\}$  in the execution order, where n is the total number of the events.

- $a_i$ , where  $i \in [1, n]$ , represents the memory address involved in  $e_i$ .

Next, we present the precise definition of  $\alpha_{in}(e_i)$  as:

$$\alpha_{in}(e_i) := \left(\exists x \in [0, i) \mid \phi\left(a_x, a_i\right)\right) \land \left(\forall y \in (x, i) \mid \neg \phi\left(a_x, a_y\right)\right) \land \sum_{z=x+1}^{i-1} \left(set(a_z) = set(a_i)\right) < \mathsf{K} \quad (7)$$

Per a memory event  $e_i$ , we first search its parent trace for the closest event  $e_x$  before  $e_i$ , who and  $e_i$  may map to the same cache line, l, by calling the function  $\phi$  (Equation 1). Second, each in-between event  $e_y$  should not access the same line l. The third sub-constraint relies on the cache replacement policy. Without loss of generality, we leverage the N-way set-associative cache and the LRU replacement policy. So, we count the number of addresses visited between  $e_x$  and  $e_i$ . Moreover, these addresses must associate with the same cache set to  $a_i$ . More importantly, such a number has to be less than the cache associativity K. This sub-constraint is to prevent from evicting the  $a_x$  data out of the cache, to promise a cache hit for  $e_i$ .

Note that our leak analysis differs from SpecuSym [Guo et al. 2020] in two aspects. First, it addresses all memory events on an *out-of-order* path, whereas SpecuSym will not analyze the cache behaviors of speculated events. Second, SpecuSym reasons for the sequentially executed events in speculation. Our new leak analysis can even analyze the speculated events in an *out-of-order* manner, and we show the result in experiments.

#### 5 EVALUATION

This section evaluates SymO<sub>3</sub> with a set of real-world benchmarks. We implement SymO<sub>3</sub> on the latest KLEE 2.0 [Cadar et al. 2008] and LLVM 6.0 [Lattner and Adve 2004]. SymO<sub>3</sub> adds four new components into the original KLEE framework.

## 5.1 Benchmarks and Research Questions

We use a diverse set of 24 benchmarks collected from recent works [Chattopadhyay et al. 2017; Guo et al. 2018, 2020; Gysi et al. 2019; Wang et al. 2020; Wu and Wang 2019] for the evaluation of SymO<sub>3</sub>. These C benchmarks consist of cipher programs, elliptic curve computation programs, worst-case execution time benchmarks, embedded media computation benchmarks, authenticating library code, GDK library code, etc.

Table 2 provides more information of the benchmarks. For each one, we have the benchmark name (**Name**), its origin (**Source**), the lines of C code (**LoC**), the number of memory visit events (#.**MemV**), and the length of sensitive input in bytes (#.**In**). #.**In** also indicates the size of the symbolic input. In each benchmark, we use the klee\_make\_symbolic function to initialize the sensitive input into symbolic value and compile the program into LLVM bitcode.

We conduct the experiments on an Amazon EC2 c5.12xlarge instance, running the Ubuntu 16.04 64-bit Server Linux with a 48-core vCPU and 96GB RAM. The time threshold for running each benchmark is twelve hours. To evaluate  $SymO_3$  against these benchmarks, we design the following three research questions:

- **RQ1**: Is SYMO<sub>3</sub> capable of detecting the cache timing leaks by its software-based analysis?

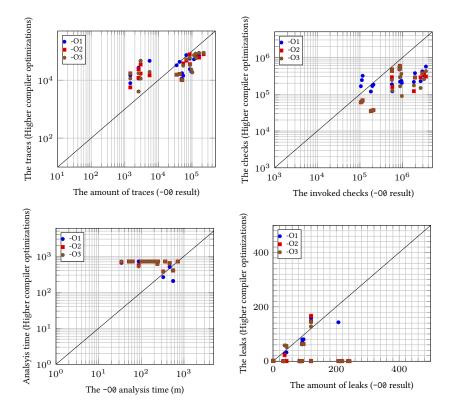

- **RQ2**: Does program transformation, e.g., compiler optimization, have a significant effect on the SymO<sub>3</sub> detection result?

- RQ3: Is SYMO3 also able to support speculative execution during its dynamic analysis?

### 5.2 The Leak Detection

5.2.1 The Configurations. In this evaluation, we use two set-associative caches: a 32 KB 4-way cache and a 32 KB 8-way cache, namely 32K4W and 32K8W in the **Cache** column of Table 3. In both caches, each cache line has the 64-byte capacity. These cache statistics are close to the L1 data cache parameters in modern processors like Intel Skylake [Intel 2016] series. Thus, we deem that they are reasonable settings.

We configure the *reorder buffer size* to be **32**, **64**, and **128**, as shown by the *RBS* value at the top row of Table 3. We use this variant to test the *RBS* impact on the leak detection. Note that the

| Name     | Source                   | LoC   | #.MemV | #.In | Name     | Source                        | LoC | #.MemV | #.In |

|----------|--------------------------|-------|--------|------|----------|-------------------------------|-----|--------|------|

| AES      | [LibTomCrypt 2019]       | 1,838 | 898    | 16   | fixfrac  | [libfixedtimefixedpoint 2017] | 63  | 28     | 59   |

| AES      | [mbedTLS 2017]           | 281   | 245    | 272  | hash     | [Rapier and Bennett 2008]     | 320 | 5297   | 64   |

| adpcm    | [Gustafsson et al. 2010] | 916   | 426    | 24   | keyvalue | [GDK 2018]                    | 62  | 18     | 4    |

| blowfish | [LibTomCrypt 2019]       | 467   | 321    | 8    | lblock   | [Dinu et al. 2015]            | 949 | 1233   | 10   |

| Camellia | [Tegra 2018]             | 1,324 | 10235  | 16   | ocb      | [LibTomCrypt 2019]            | 377 | 260    | 28   |

| chacha20 | [LibTomCrypt 2019]       | 776   | 6870   | 36   | PRESENT  | [Dinu et al. 2015]            | 215 | 57     | 19   |

| chaskey  | [Dinu et al. 2015]       | 255   | 192    | 32   | Salsa    | [Tegra 2018]                  | 279 | 481    | 28   |

| DES      | [glibc 2019]             | 547   | 687    | 16   | Seed     | [Tegra 2018]                  | 487 | 1753   | 16   |

| DES      | [Libgcrypt 2018]         | 337   | 984    | 8    | str2key  | [OpenSSL 2019]                | 371 | 89     | 16   |

| ecc      | [FourQLib 2020]          | 224   | 251    | 320  | stc      | [Lee et al. 1997]             | 494 | 242    | 1024 |

| encoder  | [LibTomCrypt 2019]       | 134   | 37     | 100  | trie     | [freeradius 2020]             | 162 | 51     | 32   |

| FCrypt   | [Dellinger et al. 2011]  | 621   | 798    | 12   | unicode  | [GDK 2018]                    | 839 | 22     | 4    |

Table 2. The benchmark information: Name, Source, Lines of Code (LoC), the Number of Memory Visit Operations (#.MemV), and the length of each Sensitive Input (#.In) in bytes.

reorder buffer in Intel Skylake [Intel 2016] has 224 entries in total. Since each LLVM instruction may correspond to multiple binary instructions [Poeplau and Francillon 2019] and even more microinstructions [Abel and Reineke 2019], our three *RBS* settings are comparable to the *reorder buffer size* in real-world processors. Also, we use the -00 compiler optimization level for the benchmark compilation in this evaluation.

For each benchmark, we record the analysis time in minutes (Time (m)), the number of *out-of-order* traces (#.Trace) derived from in-order executions, and the number of detected leaks (#.C/D) in Table 3. The leak introduced by *out-of-order* execution may exhibit two forms. We name the first one as *consistently different*, which means the new behavior is always different — e.g., always-hit in *in-order* execution but always-miss in *out-of-order* execution, and vice versa. We call the second type *divergently different*, which means the new behavior could be cache-hit under some inputs but cache-miss under some other inputs. Table 3 uses #.C/D to distinguish such two leak types. *C-type* leaks solely ascribe from the *out-of-order* schedules, and *D-type* leaks root from the blend of *out-of-order* influences and the sensitive inputs.

5.2.2 The Results. Table 3 presents the experimental results. Overall, among all the RBS settings, SYMO<sub>3</sub> can detect leaks in five programs AES [LibTomCrypt 2019], AES [mbedTLS 2017], DES [Libgcrypt 2018], FCrypt [Dellinger et al. 2011], and Seed [Tegra 2018]. We summarize our experimental findings in four points.

First, SYMO<sub>3</sub> found no *C-type* leaks in all programs. This fact implies, in most cases, the *out-of-order* execution poisons the input data to form subtle leaks rather than directly causing leaks by the *out-of-order* schedules. Also, the used -00 option avoids aggressive transformation in the compilation, which preserves the original memory-access patterns as much as possible. To investigate if the optimized compilation could cause any experimental difference, we conduct a comparison in Section 5.3.

Second, generally, the total analysis time, the amount of *out-of-order* traces, and the number of detected leaks all rise in line with the increasing *RBS* size. It is because larger *RBS* allows more instructions to enter the *out-of-order* window, which results in potentially vaster reorder state space. However, compared to the sharply raised number of #.Trace, the increasing rate of leaks and analysis time is gentle. On the one hand, SYMO<sub>3</sub> analyzes the traces efficiently, thus costing tolerable time overhead. On the other hand, many traces cannot attribute to leaks, and SYMO<sub>3</sub> precisely eliminates them to retain a minimum set of leaks.

Third, the increased cache associativity does not always correspond to more leaks. In AES [LibTom-Crypt 2019], the 32K8W cache results in fewer leaks while in DES [Libgcrypt 2018], all the results

Table 3. The leak detection results under three RBS settings

|                                        |                |          | RBS:32  |       |          | RBS: <b>64</b> |       | RBS:128  |         |       |

|----------------------------------------|----------------|----------|---------|-------|----------|----------------|-------|----------|---------|-------|

| Name                                   | Cache          | Time (m) | #.Trace | #.C/D | Time (m) | #.Trace        | #.C/D | Time (m) | #.Trace | #.C/D |

|                                        | 32K4W          | 87.03    | 54837   | 0/36  | 105.02   | 96232          | 0/42  | 101.30   | 102304  | 0/42  |

| AES[LibTomCrypt 2019]                  | 32K8W          | 180.33   | 68114   | 0/30  | 208.11   | 115546         | 0/42  | 245.15   | 128867  | 0/42  |

| -                                      | 32K4W          | 202.93   | 100658  | 0/31  | 365.68   | 106940         | 0/35  | 363.76   | 110803  | 0/91  |

| AES[mbedTLS 2017]                      | 32K4W          | 125.79   | 59846   | 0/85  | 232.14   | 89211          | 0/85  | 221.70   | 93237   | 0/91  |

|                                        | 32K4W          | 24.88    | 49093   | 0/83  | 30.83    | 67902          | 0/83  | 32.17    | 85562   | 0/91  |

| adpcm[Gustafsson et al. 2010]          | 32K4W          | 20.64    | 25156   | 0/0   | 29.01    | 33888          | 0/0   | 30.19    | 45758   | 0/0   |

| -                                      | 32K4W          | < 0.01   | 1       | 0/0   | < 0.01   | 1              | 0/0   | < 0.01   | 1       | 0/0   |

| chaskey[Dinu et al. 2015]              | 32K4W          | < 0.01   | 1       | 0/0   | < 0.01   | 1              | 0/0   | < 0.01   | 1       | 0/0   |

|                                        | 32K4W          | 10.47    | 18470   | 0/0   | 11.32    | 21169          | 0/0   | 12.08    | 22369   | 0/0   |

| blowfish[LibTomCrypt 2019]             | 32K8W          | 10.47    | 18470   | 0/0   | 10.81    | 21169          | 0/0   | 11.74    | 22369   | 0/0   |

|                                        | 32K4W          | 720      | 17084   | 0/0   | 720      | 33686          | 0/0   | 720      | 39870   | 0/0   |

| Camellia[Tegra 2018]                   | 32K8W          | 720      | 24603   | 0/0   | 720      | 46205          | 0/0   | 720      | 52830   | 0/0   |

|                                        | 32K4W          | 0.48     | 1       | 0/0   | 0.51     | 1              | 0/0   | 0.83     | 1       | 0/0   |

| chacha20[LibTomCrypt 2019]             | 32K8W          | 0.48     | 1       | 0/0   | 0.51     | 1              | 0/0   | 0.83     | 1       | 0/0   |

|                                        | 32K4W          | 189.94   | 1       | 0/0   | 208.08   | 1              | 0/0   | 204.17   | 1       | 0/0   |

| DES[OpenSSL 2019]                      | 32K4W          | 158.94   |         | 0/0   | 197.29   |                | 0/0   | 254.50   |         | 0/0   |

|                                        |                |          | 1       | _     |          | 1              |       |          | 1       |       |

| DES[glibc 2019]                        | 32K4W<br>32K8W | 1.17     | 1       | 0/0   | 1.62     | 1              | 0/0   | 2.10     | 1       | 0/0   |

|                                        |                | 1.18     | 1 170   | 0/0   | 1.26     | 1 25.02        | 0/0   | 2.07     | 1       | 0/0   |

| DES[Libgcrypt 2018]                    | 32K4W          | 34.30    | 1459    | 0/120 | 39.87    | 2563           | 0/120 | 52.02    | 2962    | 0/120 |

|                                        | 32K8W          | 62.83    | 1459    | 0/120 | 73.34    | 2563           | 0/120 | 74.83    | 2962    | 0/120 |

| ecc[FourQLib 2020]                     | 32K4W          | < 0.01   | 1       | 0/0   | < 0.01   | 1              | 0/0   | < 0.01   | 1       | 0/0   |

|                                        | 32K8W          | < 0.01   | 1       | 0/0   | < 0.01   | 1              | 0/0   | < 0.01   | 1       | 0/0   |

| encoder[LibTomCrypt 2019]              | 32K4W          | < 0.01   | 1       | 0/0   | < 0.01   | 1              | 0/0   | < 0.01   | 1       | 0/0   |

|                                        | 32K8W          | < 0.01   | 1       | 0/0   | < 0.01   | 1              | 0/0   | < 0.01   | 1       | 0/0   |

| FCrypt[Dellinger et al. 2011]          | 32K4W          | 327.45   | 49252   | 0/92  | 525.39   | 50722          | 0/92  | 558.74   | 51304   | 0/92  |

| , , , -[                               | 32K8W          | 238.05   | 34964   | 0/92  | 389.18   | 42909          | 0/96  | 464.43   | 43803   | 0/96  |

| fixfrac[libfixedtimefixedpoint 2017]   | 32K4W          | 0.02     | 1       | 0/0   | 0.02     | 1              | 0/0   | 0.02     | 1       | 0/0   |

| - 12x - Go[innineatimethicaponit 2017] | 32K8W          | < 0.01   | 1       | 0/0   | 0.02     | 1              | 0/0   | 0.02     | 1       | 0/0   |

| hash[Rapier and Bennett 2008]          | 32K4W          | 19.45    | 1       | 0/0   | 25.27    | 1              | 0/0   | 35.30    | 1       | 0/0   |

| masii[Kapier and Bermett 2000]         | 32K8W          | 26.32    | 1       | 0/0   | 32.06    | 1              | 0/0   | 42.89    | 1       | 0/0   |

| keyvalue[GDK 2018]                     | 32K4W          | < 0.01   | 1       | 0/0   | < 0.01   | 1              | 0/0   | < 0.01   | 1       | 0/0   |

| Keyvalue[GDK 2016]                     | 32K8W          | < 0.01   | 1       | 0/0   | < 0.01   | 1              | 0/0   | < 0.01   | 1       | 0/0   |

| lblock[Dinu et al. 2015]               | 32K4W          | 600.94   | 11078   | 0/0   | 720      | 11078          | 0/0   | 698.04   | 11078   | 0/0   |

| IDIOCK[Diliti et al. 2013]             | 32K8W          | 1.11     | 1       | 0/0   | 1.44     | 1              | 0/0   | 1.24     | 1       | 0/0   |

| ach[LibTomCwmt 2010]                   | 32K4W          | < 0.01   | 1       | 0/0   | < 0.01   | 1              | 0/0   | < 0.01   | 1       | 0/0   |

| ocb[LibTomCrypt 2019]                  | 32K8W          | < 0.01   | 1       | 0/0   | < 0.01   | 1              | 0/0   | < 0.01   | 1       | 0/0   |

| DDECENTED: 1 1 0015]                   | 32K4W          | 1.06     | 1       | 0/0   | 1.10     | 1              | 0/0   | 1.10     | 1       | 0/0   |

| PRESENT[Dinu et al. 2015]              | 32K8W          | 0.68     | 1       | 0/0   | 1.57     | 1              | 0/0   | 0.68     | 1       | 0/0   |

| 0.1 [7] 0040]                          | 32K4W          | 0.04     | 1       | 0/0   | 0.05     | 1              | 0/0   | 0.08     | 1       | 0/0   |

| Salsa[Tegra 2018]                      | 32K8W          | 0.04     | 1       | 0/0   | 0.05     | 1              | 0/0   | 0.09     | 1       | 0/0   |

| O UET COALS                            | 32K4W          | 117.42   | 55109   | 0/207 | 138.12   | 86954          | 0/210 | 149.86   | 132902  | 0/214 |

| Seed[Tegra 2018]                       | 32K8W          | 720      | 85365   | 0/219 | 720      | 163266         | 0/237 | 720      | 223443  | 0/242 |

| . Fr                                   | 32K4W          | < 0.01   | 1       | 0/0   | < 0.01   | 1              | 0/0   | < 0.01   | 1       | 0/0   |

| stc[Lee et al. 1997]                   | 32K8W          | < 0.01   | 1       | 0/0   | < 0.01   | 1              | 0/0   | < 0.01   | 1       | 0/0   |

|                                        | 32K4W          | < 0.01   | 1       | 0/0   | 0.01     | 1              | 0/0   | < 0.01   | 1       | 0/0   |

| trie[freeradius 2020]                  | 32K8W          | < 0.01   | 1       | 0/0   | 0.01     | 1              | 0/0   | < 0.01   | 1       | 0/0   |

|                                        | 32K4W          | 11.18    | 162318  | 0/0   | 22.01    | 222578         | 0/0   | 34.64    | 290581  | 0/0   |

| unicode[GDK 2018]                      | 32K8W          | 7.08     | 112651  | 0/0   | 8.66     | 147254         | 0/0   | 15.25    | 172955  | 0/0   |

|                                        | 32             | ,        | -12001  | 0, 0  | 0.00     | - 1, 201       | 0,0   | 1 10.20  | -,-,    | 0, 0  |

are the same. In another AES [mbedTLS 2017], 32K8W brings two more leaks under RBS:32; however, the results are the same under both RBS:64 and RBS:128. By contrast, FCrypt suffers from slightly more leaks under 32K8W with RBS:64 and RBS:128 but no difference with RBS:32. Moreover, SYMO $_3$  detects more leaks under 32K8W cache in Seed [Tegra 2018]. Intuitively, larger cache associativity means more cache lines per set, which may reduce the eviction risk for an address. However, the tradeoff is that more memory addresses can now map to the same cache set. After studying the bitcode, we find that the in-between instructions of two same-address memory events may directly impact the cache state. Thereby, the results of changed cache associativity values vary against per-program semantics.

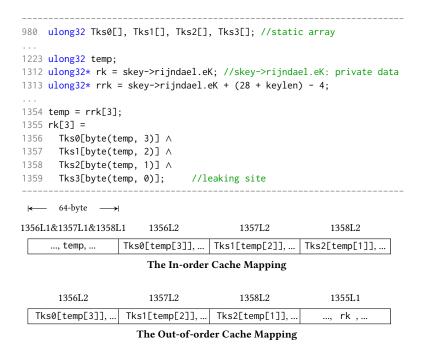

Fourth, the timing leaks from *out-of-order* execution are hard to detect though they can appear in various caches. SymO<sub>3</sub> finishes 23 of the 24 programs within the 12-hour threshold. One exception is Camellia [Tegra 2018], which has the most significant number of 10,235 memory read events, and SymO<sub>3</sub> found no leaks until timeout. The other one is Seed [Tegra 2018], which exposed more than 200 leaks before timeout under 32K8W. Moreover, out of the 144 experiments which test the combination of different cache associativity and *RBS*, only 30 experiments expose leaks. Among the 3.9+ million traces of all the 144 experiments, the leaks only appear in less than 0.1% of the total traces. This phenomenon explicitly illustrates the elusiveness of the leaks, which also highlights the detection ability of SymO<sub>3</sub>.